Conditional Branch instruction in AVR Microcontroller

In terms of assembly language programming, the most important and fundamental aspect is the ability to control the flow of a program. If we are controlling program flow, it means that we instruct the microcontroller to jump from one address to another address in the program. This process is referred to as branching. Without this feature, the instruction will be sequentially executed by the microcontroller in their memory as long as they run out. If we try to write a nontrivial program without conditional branching, it will be extremely difficult, but the process is not impossible. With the help of the registers, we can understand the instruction of an AVR microcontroller, which are described as follows:

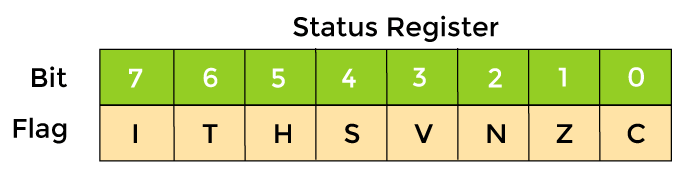

Status Register (SReg)

The status register is also called a flag register or condition code register in the AVR microcontroller. It is used for certain programming purposes by the programmer. It contains information related to the state of processor. This register is 8-bit. It contains 8 flags that are updated on the basis of the result of previous instruction. With the help of 6 bits (from bit 0 to bit 5), the conditional flag is represented that are V, S, Z, N, C, and H.

In the status register, the representation of 8 bits is described as follows:

Here, the use of data bits are described as follows:

Bit 0: It is a carry flag represented by C, also known as D0.

Bit 1: It is a Zero flag represented by Z, also known as D1.

Bit 2: It is a Negative flag represented by N, also known as D2.

Bit 3: It is a Two’s complement overflow flag represented by V, also known as D3.

Bit 4: It is a Sign Bit represented by S, also known as D4.

Bit 5: It is a Half carry flag represented by H, also known as D5.

Bit 6: It is a Bit copy storage represented by T, also known as D6.

Bit 7: It is a Global Interrupt Enable represented by I, also known as D7.

Carry Flag

The carry flag is also known as the C flag. Suppose we are performing n bit arithmetic or logical operations. The carry flag will be set with value 1 if the operation generates a result with more than n bits. Otherwise, the carry flag will be reset with a value 0.

Zero Flag

This flag is also known as the Z flag. This flag will be set with value 1 if the result of an arithmetic operation is zero. If the result is not zero, the flag will be reset with a value 0. In other words, we can express zero flags like this:

Negative Flag

This flag is also known as the N flag. Here we will use the sign bit D7, which is used to show the binary representation of signed numbers. The flag will be set with value 1, and the result will be negative if the D7 bit shows the value 1. This flag will be reset with value 0, and the result will be positive if the D7 bit shows the value 0. In other words, we can express a negative flag like this:

Overflow Flag

This flag is also known as the V flag. The overflow flag will be set with value 1 if the output of a signed number operation is very large. Due to this, the high order will be overflow into the sign bit. In another case, the overflow flag will be reset with value 0.

Sign Flag

This flag is also known as the S flag. After any logical operation or arithmetic operation, if D7 shows the value 1, then 1 will indicate the negative number and also shows that the sign flag is now set. If the D7 shows the value 0, then 0 will indicate the positive number and show that the sign flag is reset.

Half Carry Flag

This flag is also known as the H flag. While the operation of ADD or SUB operation, the half carry flag will be set if there is a carry from D3 to D4.

The following table shows the various types of conditional branch instructions and its explanation:

| Instruction | Explanation | Flag Status |

|---|---|---|

| BREQ | BREQ refers to the “Branch if Equal“. It is a type of conditional relative branch. If zero flag (Z) is set, this instruction will test the Z and branches relative to PC (Program counter). Suppose there are two registers, D (destination register) and S (source register), containing signed or unsigned binary numbers. The branch will have occurred if the binary number of register D and register S are equal to each other. The BREQ relatively to program counter in either direction, which is PC – 63 ≤ destination ≤ PC + 64. Here offset is represented with the help of k. | Branch if Z = 1 |

| BRNE | BRNE refers to the “Branch if not Equal“. It is a type of conditional relative branch. If zero flag (Z) is cleared, this instruction will test the Z and branches relative to PC (Program counter). Suppose there are two registers, D (destination register) and S (source register), containing signed or unsigned binary numbers. The branch will have occurred if the binary number of register D and register S are not equal to each other. | Branch if Z = 0 |

| BRSH | BRSH refers to the “Branch if Same or Higher (Unsigned)“. It is a type of conditional relative branch. If the carry flag (C) is cleared, this instruction will test the C and branches relative to PC (Program counter). Suppose there are two registers, D (destination register) and S (source register), containing unsigned binary numbers. The branch will have occurred if the unsigned number of register D is greater than or equal to the unsigned number of register S. The BRSH relatively to program counter in either direction, which is PC – 63 ≤ destination ≤ PC + 64. Here offset is represented with the help of k. | Branch if C = 0 |

| BRLO | BRSH refers to the “Branch if Lower“. If carry flag (C) is set, this instruction will test the C and branches relative to PC (Program counter). Suppose there are two registers, D (destination register) and S (source register), containing unsigned binary numbers. The branch will have occurred if the unsigned number of register D is smaller than the unsigned number of register S. | Branch if C = 1 |

| BRLT | BRSH refers to the “Branch if Lower“. If a signed flag (S) is set, this instruction will test the S and branches relative to PC (Program counter). Suppose there are two registers, D (destination register) and S (source register), containing the signed binary numbers. The branch will have occurred if the signed number of register D is less than the signed number of register S. The BRLT relatively to program counter in either direction, which is PC – 63 ≤ destination ≤ PC + 64. Here offset is represented with the help of k. | Branch if S = 1 |

| BRGE | BRGE refers to the “Branch if Greater or Equal“. If a signed flag (S) is cleared, this instruction will test the S and branches relative to PC (Program counter). Suppose there are two registers, D (destination register) and S (source register), containing the signed binary numbers. The branch will have occurred if the signed number of register D is greater than or equal to the signed number of register S. | Branch if S = 0 |

| BRVS | BRVS refers to the “Branch if Overflow set“. If overflow flag (V) is set, this instruction will test the V and branches relative to PC (Program counter). | Branch if V = 1 |

| BRVC | BRVC refers to the “Branch if Overflow cleared“. If the overflow flag (V) is cleared, this instruction will test the V and branches relative to PC (Program counter). | Branch if V = 0 |